# Genesys を用いたRFアンプ設計-1

## 線形解析による安定性解析と整合回路の設計

### はじめに

小信号のRFアンプを作るためには、以下の表に挙げるような要素を考慮しながら設計を行う必要があり、チューニング、最適化などを行いながら比較的複雑な計算を行う必要があります。このアプリケーションノートシリーズでは、1.9GHz LNA設計を例にとり、Genesysを利用した基本的なRFアンプの設計方法について安定性の吟味から、相互変調ひずみ解析までを順を追って説明していきます。

本アプリケーションノートは、安定性 解析と整合について説明します。 ーツセレクタで必要な部品が登録され ていることを確認してから、

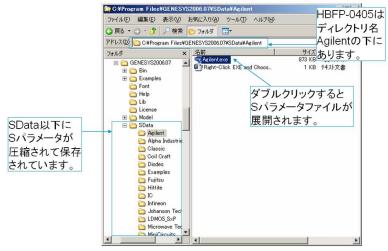

C:\ProgramFiles\GENES\YS2006. XX\YSDa ta\Pagilent (XX は Genesys2006 のリビジョン) ディレクトリの内部の Agilent. exe をダブルクリックし、ファイルを展開します。(これらのデバイスは現在 Avago Technologies 社より販売されていますが、Genesys2006.07 現在、ライブラリ名は分社前の Agilent になっております。)

以上の作業を終えると、HBFP-0405 の S

パラメータが利用できるようになります。

なお、DC バイアス設定、高調波解析には、トランジスタ真性部および部品パッケージ(リード含む)のパラメータが抽出された SPICE ファイルを用意する必要があります。この SPICE ファイルは、Avago Technologies 社のホームページより、無償でダウンロードすることができます。詳細は、本アプリケーションノートシリーズ "HERBEC による大信号解析"をご覧下さい。

### デバイスSパラメータのイン ストール

このアプリケーションノート上では、Avago Technologies 社の LNA 用表面実装 BJT である HBFP-0405 を利用しております。Genesys には、各部品メーカーの S パラメータファイルが含まれており、今回利用する HBFP-0405 の S パラメータとして、DC バイアス設定 Vce=2Vにおける Ic=2mA の場合と 5mA の場合の各ファイルが用意されています。

Sパラメータは、はじめは圧縮された形で保存されています。 初めて Avago Technologies 社の S パラメータを Genesys 上で利用する場合には、まずパ

図1 Sパラメータファイルのインストール

図2 インストールされたSパラメータファイル

### 安定性の解析

### デバイスそのものの特性をみる

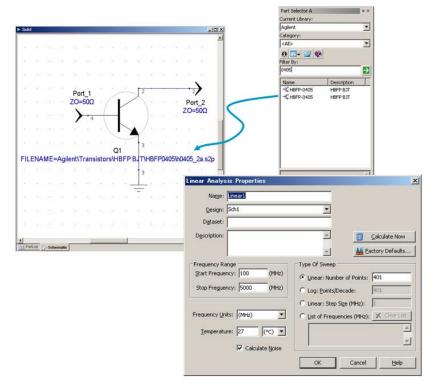

まず、ネットワークアナライザとノイズフィギィアアナライザによって測定された HBFP-0405 の特性を、さきほどインストールされた S パラメータを利用して解析します。パーツセレクタ内でライブラリに "Agilent"を指定し、フィルタに 0405 と入力すると、HBFP-0405のSパラメータが選択できます。ここでは図 3 のように Ic=2mA 用の $h0405_2a$  を選択します。

ベースをポート1、コレクタをポート 2とし、エミッタを接地します。 解析に利用するシミュレーションエン

解析に利用するシミュレーションエン ジンは線形解析(Linear Analysis)で、 掃引周波数は 100MHz から 5GHz としま す。

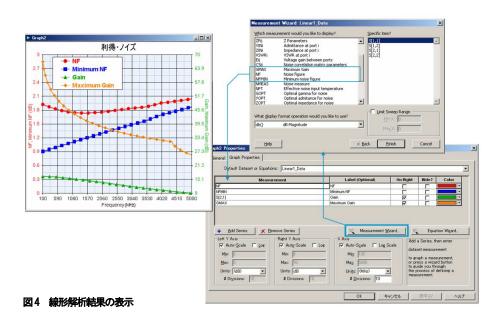

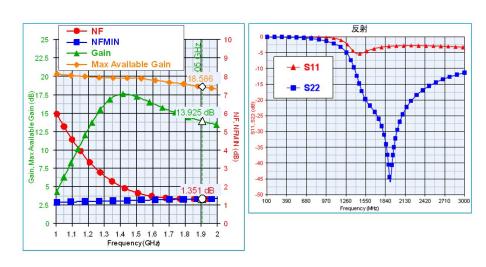

解析後に、図4のように最小NF、NF、 最大有効利得、利得を直交座標に表示 させます。

これらは、グラフプロパティ内の" Measurement Wizard"より選択します。

最小NFとNF、最大有効利得と実際の利得にそれぞれ大きな開きがあることがわかります。

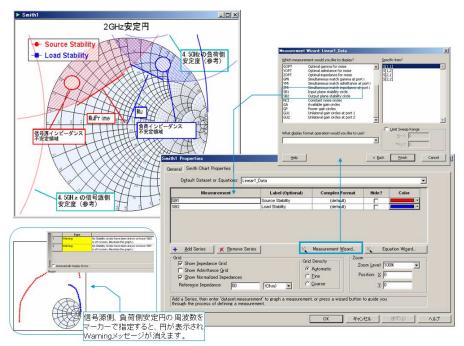

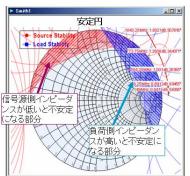

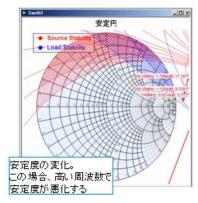

次に、入出力インピーダンスによる安 定度の変化をスミスチャート上に表示 させます。

図 5 に示されているのは、2GHz の安定 円と 4.5GHz の安定円です。2GHz の安定 円では、入力、出力のインピーダンス の設定によっては、不安定な領域(斜 線で表示)が存在します。一方で、 4.5GHz の安定円はスミスチャートの内 部と交わらないので、入出力にどのよ うな受動素子が整合回路として利用さ れても安定に動作することがわかりま す。(安定円を表示させるためには、 安定円中心軌跡上をクリックし、周波 数を指定する必要があります。)

スミスチャートの特性インピーダンス (中心)から信号源側安定円(SB1)、 負荷側安定円(SB2)への最短距離はそれぞれ MuPrime, Mu と呼ばれ、図形的な 安定性を示す指標になっいます。

図3 Sパラメータファイルの呼び出しと線形解析

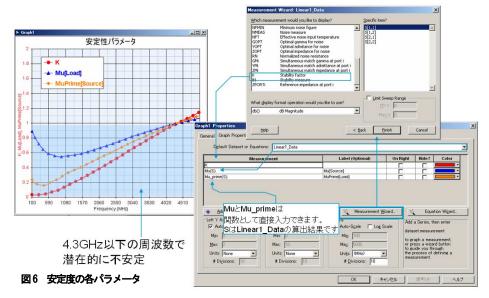

この MuPrime, Mu を Genesys に算出させ、直交座標上で安定性の周波数変化をみます。

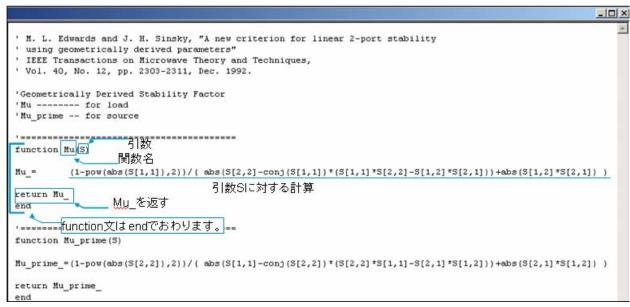

### ユーザ関数 Mu\_Prime(), Mu()の定義

MuPrime, MuはGenesysの内部関数として定義されていないため、ユーザ関数として用意する必要があります。

図7に示されたように、引数をSとし、MuPrime と Mu の計算を行い、その結果を返し値とする関数を数式エディタに入力します。(ユーザ関数は、ユーザライブラリとして登録することも可能です。)

この関数を利用してグラフを描くには、 直交座標プロパティで参照するデータ セットを選択し (Linear1\_Data)、その データセット内の S を引数として MuPrime(S), Mu(S)を直接入力します。 (このときのSとはLinear1\_Dataのデ ータセットのSを指します。)

図 6 では、ローレットの安定係数 K ファクタもあわせて表示させています。

MuPrime, Mu, K 共に 1 以上で安定である ことを示します。

このことから 4.3 GHz 以下の周波数はでは、潜在的に不安定なことが分かり、 先ほどの図 5 において 2GHz で不安定な 領域が存在し、4.5 GHz で安定なことが 裏付けられました。

図5 信号源・負荷側安定円の表示

図7 MuPrime とMuのユーザ関数設定

#### 不安定性の要因と安定にさせる方法

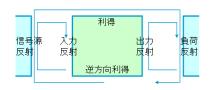

ここで、不安定にさせる要因について、 簡単にまとめてみます。今回のような 2ポートデバイスには下図のような 3 つの信号のループが存在します。

これらのループによって作られる不要なフィードバックにより、ループ利得が 1 以上になると、発振の可能性がでてきます。このループ利得を低減させることで、系全体を安定にさせることができます。

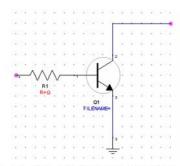

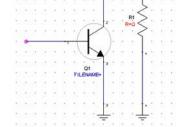

ループ利得を低減させるためには抵抗性の部品を利用します。基本的な回路を図8に示しました。この回路図の概念は、図9の広帯域の安定円軌跡をみると理解しやすいです。

図9の信号源側の安定円でスミスチャートと重なる部分はインピーダンスの 比較的低い領域を指しています。この 領域を安定にするためには、インピー ダンスを高くする方向に持っていく必 要があります。そこで図8の左に示し た直列に抵抗を入れるトポロジをつか います

図9の負荷側の安定円がスミスチャートと重なる部分は、インピーダンスの高い領域を示します。今度は先ほどと逆に、安定にするためにはインピーダンスを低くする必要があるため、図8の右側に示すように抵抗をコレクタとグラウンドに並行に入れるトポロジを使います。

一般的に、入力に抵抗を入れてループ 利得を下げる方法は、パワーアンプに 利用され、出力に抵抗を入れる方法は LNA に利用されます。LNA で前者を利用 すると、抵抗で損失されるエネルギー から雑音が生じてしまうためです。

先ほどの直交座標に表示した MuPrime, Mu, K より、周波数が高くなるにつれて 安定度が増す傾向がわかりました。つ

トランジスタの前段に抵抗を追加

トランジスタの後段に抵抗を追加

図8 安定化回路の基本トポロジ

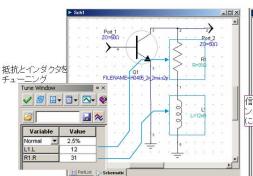

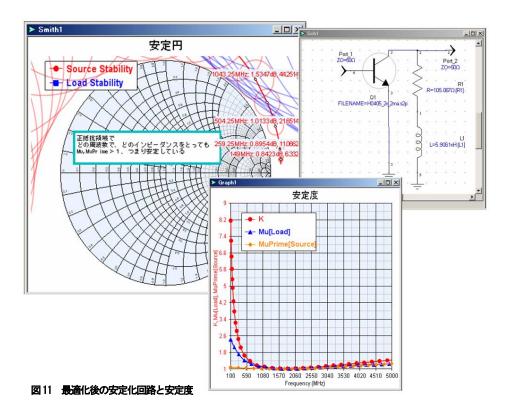

R=31Ω、L=12nH時の安定円

図9 安定化回路のチューニングと広帯域安定円軌跡の変化

まり、低い周波数で抵抗素子が効果を発揮するようにリアクティブな素子を利用して設計する必要があります。そこで、今回は LNA のアプリケーションのため、基本的には後者のトポロジを採用し、抵抗の先にインダクタをつけます。インダクタの代わりに、動作周波数の 1/4 波長の分布定数回路をつけても動作周波数においてオープンスタブになることから、同様の効果が得られます。

これらによる安定性の改善は、図 9 のようにチューニングを利用するとより 容易に確認できます。

#### 無条件安定化

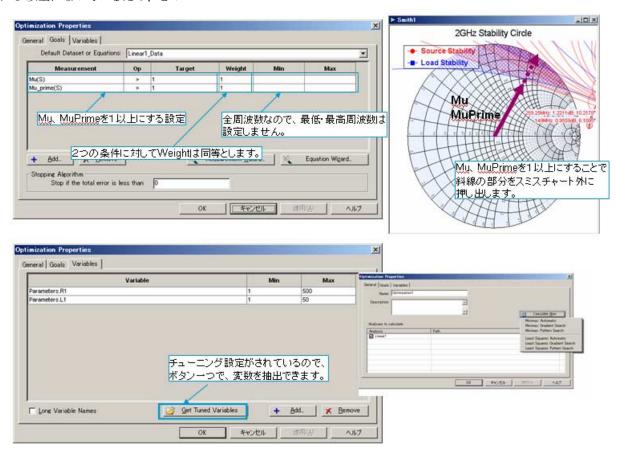

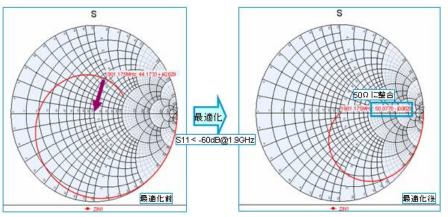

先ほど算出した MuPrime, Mu は、スミスチャートの中心 (特性インピーダンス)から安定円境界までの距離でした。これらを1以上にすることは、安定円をスミスチャート正抵抗領域から追い出すことになり、幾何学的に無条件に安定な状態を作り出します。ここでは、MuPrime, Mu を1>にするように、パラメータを最適化していく方法を紹介し

ます。(他に無条件安定な条件として、K ファクタ> 1 かつ B1>1 とする方法もあります。)

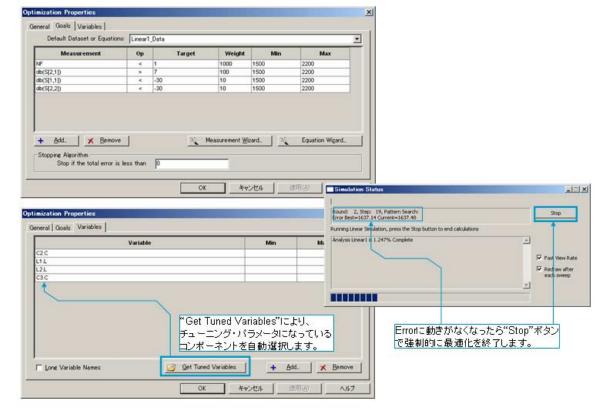

図10のように、最適化のプロパティのゴール設定タブ内でMuPrimeとMuをデータセットLinearl\_DataのSに対して計算をさせ、全周波数(100MHz から5GHz)で1以上になるように設定します。(今、線形解析の掃引周波数が100MHzから5GHzに設定されているため、全周波数を設定するために最適化ゴールの独立変数[S の場合は周波数]の最大最小値を明示的に指定する必要はありません。)

最適化されるコンポーネント R1,L1 (図 9 参照) は、チューニングの設定が既にされていれば、"Get Tuned Values"のボタンを押すことで自動的に最適化対象に設定されます。コンポーネントの値の範囲は、抵抗は  $500\Omega$ 程度、インダクタは 50nH 程度までにしておきます。

MiniMax 法 (エラー関数の最大値をが最小になるところを関数の値とする方

法)の Automatic を選択し、最適化を 実行します。

図11は、最適化の結果を示しています。 安定円とスミスチャートの中心からの 距離が1以上になっているため、どの 周波数領域でも信号源、負荷のインピーダンスによらず安定化させることができました。

### 図10 安定化回路の最適化設定

### エミッタ端子のインダクタンスの影響

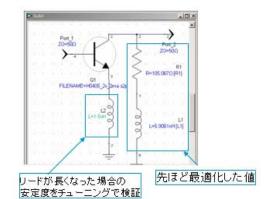

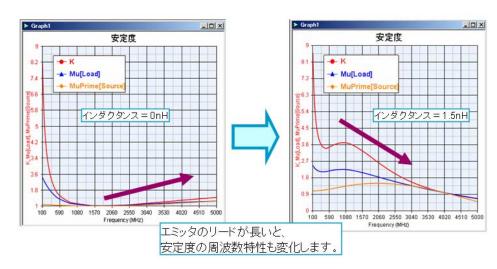

ここで、エミッタの接地度合いについて考察してみます。今回のトポロジはエミッタ接地ですが、この接地部分のリードが長くなりリアクタンス成分(インダクタンス)が増えた場合、安定度にどのような影響を与えるかについて、チューニングを利用して確認します。(図 12 参照)

図13のように、リードが長いくインダクタンス分が多いと安定度の周波数特性が変化し、高域の安定度が下がってしまいます。このことから、なるべくリードを短くし接地させることが安定度を向上させるために必要なことがわかります。

ただし、このインダクタは安定度と利得が多少犠牲になりますが、一方で負帰還の効果により IP3 と P1dB を改善する効果も持っていますので、トレードオフを考慮し、必要に応じてインダクタンスを調整する場合もあります。

図12 エミッタのインダクタンスと安定円

図13 エミッタのインダクタンス変化と安定度の周波数応答

### 整合

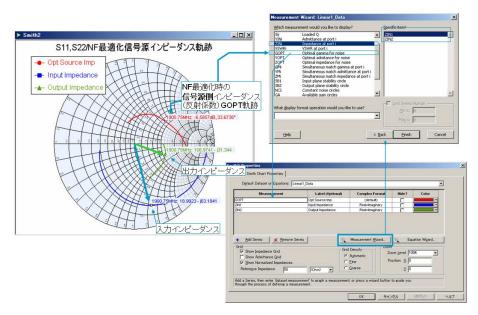

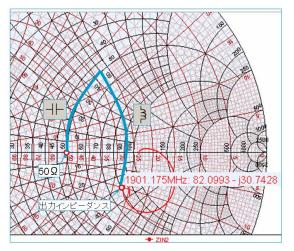

図 14 のように信号源と負荷のインピーダンスを  $50\Omega$  として、 $50\Omega$  系から見た入出力インピーダンス ZIN1 と ZIN2 をスミスチャート上で表示させると、スミスチャートの中心ら大きく外れていることがわかります。これらのインピーダンス整合を、NF の最適化を考慮しながら行います。

Genesys を利用して整合をとるために は主に2種類の方法があります。

- マルチステージの整合回路合成ツール MATCH を利用する

- 2. 整合回路のトポロジを自分で設定 し、最適化機能をもちいて定数を 算出する

この順番に説明をしていきます。

### マルチステージ整合回路合成ツール MATCH の利用

MATCH というツールは、指定したトポロジによりマルチステージの整合を取ることのできる回路合成ツールです。

#### 指定する基本項目は

- 整合を取る周波数範囲

- 信号源側、負荷側インピーダンス

- 整合回路トポロジ

- 整合を取る対象になるアンプ回路の 指定

で、簡単な操作で整合を取ることができます。

MATCH プロパティ内において以下のように設定を行った後、Section タブで対象とするアンプの回路を整合回路によりサンドイッチ状にはさみこみます。

周波数範囲:1.8GHz - 2.0GHz

インピーダンス:50Ω

トポロジ:π型

RF パスをキャパシタ指定 (ハイパス型)

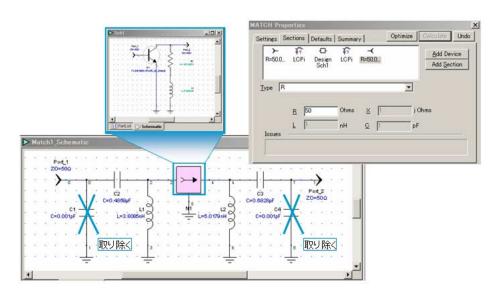

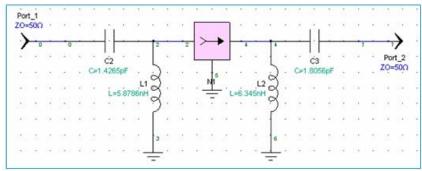

"Calculate" ボタンを押すと図 15 のような整合回路が合成され、線形解析が行われ、図 16 のような結果が表示されます。

図 14 NF 最適化信号源インピーダンスの軌跡と入出力インピーダンス

図15 MATCHが合成した整合回路

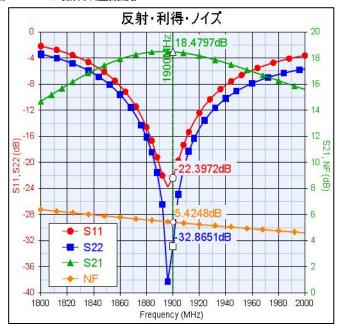

図16 MATCH整合回路の周波数応答とNF

#### 図 17 NF 最適化

合成された回路のC1 とC4 は 1.9GHz では効いてこないため、このあと取り除きます。

ここで生成された整合回路は、 $50\Omega$ の信号源、負荷に対して整合が取られていますが、NFの考慮はされていません。図 16 の結果より、1.9 GHz において利得は 18.5 dB ほどありますが、一方で NFは 5.4 dB と LNA の性能としてはあまりよくありません。

そこで、最適化によって、利得を多少落としてもNFをなるべく小さくするようにC2、C3、L1、L2を決定します。

ここに、最適化の設定を示します。(図 17参照)

周波数範囲: 1.5GHz-2.2GHz

NF < 1.3

S21 (利得) > 7

S11 (入力反射) < -30

S22 (出力反射) < -30

重み付け(Weight)は、LNA なので NF を重視し

NF>利得>反射 の順に設定します。

図 18 NF 最適化後の整合回路

図19 最終的な整合回路の周波数応答 [章:"まとめの"図28と同じ]

次に、最適化プロパティから最適化するコンポーネントを選択しやすくするために、整合回路すべてのコンポーネント(C2、C3、L1、L2)をチューニン

グパラメータにし、最適化プロパティ 内の"Get Tuned Variables"を利用 して最適化対象のコンポーネントを 自動選択します。 (複数コンポーネントのチューニング 化には、回路図のサブウィンドウをク リックし、Shift キーを押しながら、チューニングしたいコンポーネントを複 数選択し、Schematic/Make Components Tunable を実行すると便利です。)

この最適化設定では、到達されないゴールを設定しているため、最適化のエラーが0にならず収束しません。そこで、しばらくしてエラーに動きがなくなったら"Stop"ボタンで強制的に最適化を終了します。

最適化後の NF、利得と L, C の定数を図 18 に、解析結果を図 19 にそれぞれ示します。

先ほどの結果(図 16)と比べると、大幅に利得とNFが改善されていることがわかります。

これで MATCH と最適化を利用した NF を考慮した整合回路の設計は終了 です。

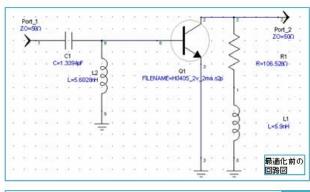

# 整合回路のトポロジを指定する場合

### 入力側の整合

次に、手動で整合回路のトポロジを指 定する場合について説明します。

ここでは、1.9GHz において NF を最小に する NF 最適反射係数 (GOPT) を利用し て、整合回路を設計します。この反射 係数は、出力側のインピーダンスが完 全に整合がとられている条件で算出さ れています。

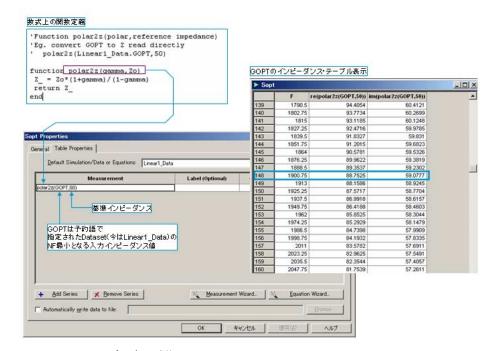

GOPT は反射係数なので、インピーダンスに変換する必要があります。極座標を50Ω系のインピーダンスに変換する関数と、その結果を表示させるテーブルを作成し、テーブル内部から1.9GHz付近のインピーダンスを読み取ります。(図20参照)

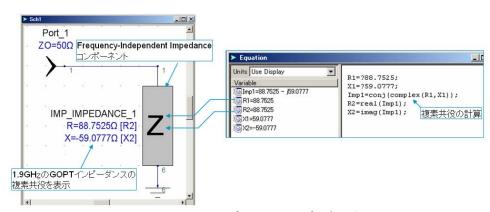

このインピーダンスは、GOPT から算出 されているため、信号源のインピーダ ンスを表しています。よって、整合を とるには図21のようにこのインピーダ ンスの複素共役をとる必要があります。

図20 GOPT のインピーダンス変換

図 21 Frequency-Independent-Impedance コンポーネントのインピーダンス表現

図22 入力インピーダンスと入力整合回路トポロジの決定

図23 入力整合回路とチューニング設定

複素共役を計算するには、conj 関数を 数式内で利用します。算出されたイン ピーダンスを回路素子として表現する ために、"Frequency-Independent Impedance"という Genesys コンポーネ ントを利用します。(図 21 参照)

図24 最適化によるS11の変化

図25 出力インピーダンスと整合回路トポロジの決定

図26-A 入力整合回路と アンプ本体

図 26-B 入出力整合回路 とアンプ

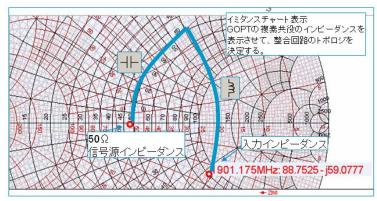

線形解析をおこない、結果表示を図 22 のようにイミタンスチャートに表示し、低い周波数をカットするために、HPF の形式をとることに決め、信号源から C (直列)  $\rightarrow$ L (並列) の順に素子をいれていく整合回路のトポロジに決定します。

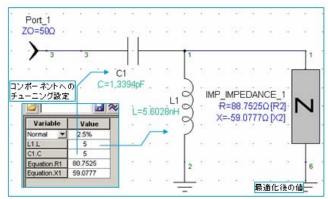

上記トポロジを図 23 のように入力し、 L1、C1 の値をチューニングできるよう に設定します。

図 24 のようにスミスチャート上で  $1.9 {\rm GHz}$  のポイントにマーカーをおき、 チューニングにより、スミスチャート の中心  $50 \Omega$ 付近にマーカーをもっていきます。

図 23 の回路に反射が 1.9GHz 付近で -60dB 以下になるように最適化を行う と、およそ

L1=5.6nH

C1=1. 34pF

の値が決定されます。

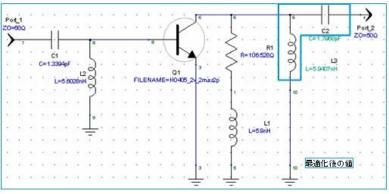

#### 出力側の整合

次に、 $1.9 \mathrm{GHz}$  における出力側のインピーダンスの整合をとります。図  $26\mathrm{-A}$  のように、さきほど算出した入力整合回路を接続した状態で、出力側のインピーダンスをイミタンスチャート上で読み取ります。今は $[82.1+30.7\,\Omega]$ となっているので、この位置から整合を取るためのトポロジを決定します。この場合も、先ほどと同様に HPF のトポロジを選択しました。

出力側の整合回路として L と C を追加し、最適化により図 26-B の L3, C2 の定数を求めます。

こ の 例 で は 、 反 射 係 数 を  $1600 \mathrm{MHz} - 2200 \mathrm{MHz}$  で $-25 \mathrm{dB}$  以下になるように設定しました。

これにより、およそ

L3=5.94nH

C2=1.8pF

の値が算出されます。

以上で、最適化は終了です。

3.山土参入口吹

図26 整合前と整合回路を追加し最適化を行った後

### まとめ

ここまでで、安定化回路を追加し、マルチステージ整合回路合成ツールや NF 最適反射係数を利用して、NF 最適化を考慮した入出力インピーダンスの整合を行いました。どちらの場合においても最終的には、ほぼ同じ回路が得られました。

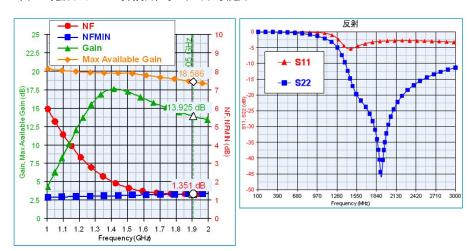

ここでは、設計された LNA の回路を改めて線形解析をし、最終的な性能を確認します。

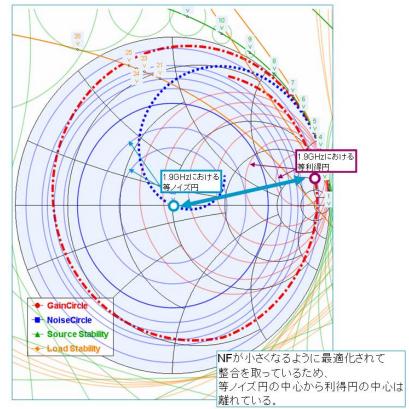

信号源側安定円 負荷側安定円 等利得円 等ノイズ円

をスミスチャート上に表示させ、安定 度と利得、NF のインピーダンスによる 変化を確認します。 (図 27 参照)

等利得円は-1,-2,-3,-4,-5,-6dB、等 / イズ円は+.25,+.5,+1 (太字),+1.5,+2,+2.5,+3,+6dB をそれぞれ表します。

スミスチャートから、 $1.9 \mathrm{GHz}$  の等ノイズ円の中心が信号源インピーダンス (スミスチャート中央= $50\,\Omega$ ) になっている一方、等利得円の中心は、 $50\,\Omega$  から離れていることがわかります。このことは図 28 の直交座標に表示させた NF と利得のグラフからも明らかで、 $1.9 \mathrm{GHz}$  で最小 NF と NF が一致している一方で、利得は最大有効利得が  $18.5 \mathrm{dB}^1$  に対して  $14 \mathrm{dB}$  ほどになっていることに対応します。

図 28 の反射特性を示した直交座標から、 出力側は反射が少なく整合が取れてい ますが、入力側は NF を最小にするため 整合を故意に取っていないことがわか

図27 完成したLNAの等利得円、等ノイズ円と安定円

図28 完成したLNAのNF、利得、反射特性

ります。

NF と利得にはトレードオフの関係が存在し、利得を大きくしようとすると、NF が悪化してしまい、またその逆も起こります。必要に応じて、さらに NF と利得のトレードオフを考慮した最適化を行います。

以上で、線形解析による LNA 設計は終 了です。

### 参考文献

[1] HBFP-0405 BJT Datasheet, Avago Technologies, Inc.

- [2] A Comparison of Various Bipolar Transistor Biasing Circuits, Application Note, [AN #1293], Avago Technologies, Inc.

- [3] 1800 to 1900 MHz Amplifiers using the HPFP-0405 and HBFP-0420 Low Noise Silicon Bipolar Transistors, Application Note, [AN#1160], Avago Technologies,

- [4] ADS "Design of a 1GHz Low Noise Amplifier", Agilent Technologies, Inc.

- [5] "Linear Active RF Circuit Design" Seminar Text, Besser Associates

- [6] Joseph F. White, High Frequency Techniques, Chapter 10:Transistor Amplifier Design, John Wiley &Sons, Inc., 2004

<sup>&</sup>lt;sup>1</sup> グラフ表示の注意点: Genesys 内部における最大有効利得計算結果の出力単位が dB10 固定のため、dB10 宣言をグラフプロパティで明示的にする必要があります。 [dB10(GMAX)]、S-para、NF などは自動的に dB 単位が割り当てられますので、この作業は不要です。

[7] 市川裕一/青木勝, GHz 時代の高周 波回路設計, 第4章ロー・ノイズ アンプの設計と製作, CQ 出版社, 2003 年第3版

### ワークスペース一覧

本アプリケーションノートで利用している Genesys ワークスペースファイルは弊社の Web よりダウンロードできます。以下の一覧は、ワークスペースファイル名と解析内容との対応を示します。

- 1. HBFP-0405 の特性 0405\_sparal.wsx

- Mu 関数設定と安定化回路 0405\_spara2.wsx

- 3. エミッタへのインダクタンスの影響

0405\_spara3.wsx

- 4. 等ノイズ円・NF 最適反射係数 0405\_spara4-x. wsx

- 5. MATCH ツール入力整合 0405match\_match1.wsx

- 6. MATCH ツール出力整合 0405\_match\_match2.wsx

- 7. NF 最適反射係数を利用した入力 整合

0405\_match1-x.wsx

8. NF 最適反射係数を利用した出力 整合

0405\_match2-x.wsx

9. 完成した線形 LNA アンプ 0405final1.wsx

すべてのワークスペースは、Genesys2006.07 を利用して作成されています。

### 改訂履歴

初版 2006 年 8 月 第 2 版 2008 年 9 月 最大有効利得表示についての訂正 アジレント・テクノロジー株式会社 本社〒192-8510 東京都八王子市高倉町 9-1 計測お客様窓口

受付時間 9:00-18:00 (土・日・祭日を除く)

TEL  $\blacksquare$  0120-421-345

(042 - 656 - 7832)

FAX■■ 0120-421-678

(042 - 656 - 7840)

Email contact\_japan@agilent.com

電子計測ホームページ

www.agilent.co.jp

記載事項は変更になる場合があります。ご発注の際にご確認ください。

${\Bbb C}$  Agilent Technologies. Inc. 2011

Published in Japan, September 21,2011

5990-9155JAJP

0000-08A